WaveShare

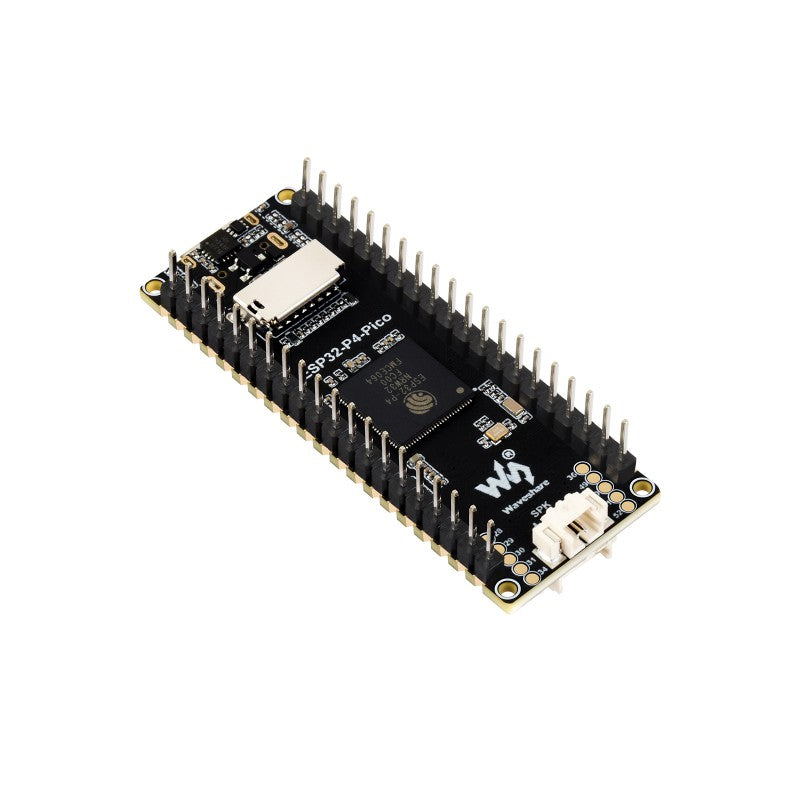

ESP32-P4-Pico Development Board

ESP32-P4-Pico Development Board

SKU:E01013-001

• Shipping cost $5 within AU, more details

• Shipping to Non-Australia, contact us

• Accept 30-day returns, see details.

In stock

Couldn't load pickup availability

Product Overview

Description

This product is a multimedia development board based on ESP32-P4. It features rich Human-Machine interfaces, including MIPI-CSI (with integrated Image Signal Processor), MIPI-DSI, SPI, I2S, I2C, LED PWM, MCPWM, RMT, ADC, UART and TWAI, etc. Additionally, it supports USB OTG 2.0 HS, and onboard 40PIN GPIO header which is compatible with some Raspberry Pi Pico HATs, enabling a wider range of application adaptability.

The ESP32-P4 adopts a 400MHz dual-core RISC-V processor and supports up to 32MB PSRAM, featuring USB 2.0, MIPI-CSI / DSI, H.264 encoder, and other peripherals, meeting the needs for low-cost, high-performance, and low-power multimedia development. It also integrates a Digital Signature Peripheral and a dedicated Key Management Unit, ensuring secure data and operations. Specifically designed for high-performance and high-security applications, the ESP32-P4-Pico meets the requirements of Human-Machine interaction, efficient edge computing, and IO expansion.

Features and Spec

- High-performance MCU with RISC-V 32-bit dual-core and single-core processors

- 128 KB HP ROM, 16 KB LP ROM, 768 KB HP L2MEM, 32 KB LP SRAM, 8 KB TCM

- Powerful image and voice processing capability. Provides image and voice processing interfaces including JPEG Codec, Pixel Processing Accelerator, Image Signal Processor, H.264 encoder

- 32MB PSRAM in the chip's package, with onboard 32MB Nor Flash

- Commonly used peripherals such as MIPI-CSI, MIPI-DSI, USB 2.0 OTG, SDIO 3.0 TF card slot, microphone, and speaker header, etc.

- Adapting 2*20 GPIO headers with 27 x remaining programmable GPIOs

- Security features: Secure Boot, Flash Encryption, cryptographic accelerators, and TRNG. Additionally, hardware access protection mechanisms help to enable Access Permission Management and Privilege Separation

Documentation

- ESP32-P4-Pico Development Board Schematic

- ESP32-P4-Pico Development Board Datasheet

- ESP32-P4 Datasheet

- ESP32-P4 Technical Reference Manual

Software

Demo